創新SOT-MRAM架構 提升新一代底層快取密度

【作者: imec】

要將自旋軌道力矩磁阻式隨機存取記憶體(SOT-MRAM)用來作為底層快取(LLC),目前面臨了三項挑戰;微縮性、動態功耗,以及可供量產且尺寸緊湊的零磁場磁矩翻轉技術。比利時微電子研究中心(imec)在2022年IEEE國際電子會議(IEDM)上提出一套創新的SOT-MRAM架構,能夠一次解決這些挑戰。

近年來,SOT-MRAM技術的開發熱度在半導體業攀升。SOT-MRAM是一種非揮發性記憶體,具備優良性能,適合用來當作嵌入式記憶體,例如高效能運算與行動裝置的三級(L3)與四級以上快取記憶體。目前的快取記憶體通常採用具備極速讀寫能力的揮發性SRAM元件。

然而,由於微縮限制,SRAM難以持續擴充位元密度,使得開發人員不得不尋求替代元件。此外,在非運作狀態下,SRAM儲存單元的散熱問題越來越嚴重,導致待機功耗增加。MRAM等非揮發性記憶體不僅有望縮小儲存單元的尺寸,利用其非揮發性,還能解決待機功耗的問題。

SOT-MRAM性能亮點:奈米級開關速度、耐久重複讀寫

SOT-MRAM由技術成熟度較高的自旋轉移力矩磁阻式隨機存取記憶體(STT-MRAM)發展而來,由於耐久性更佳,開關速度更快,因此在快取記憶體的應用潛能更大。這兩種MRAM記憶體單元的「核心」都是磁性穿隧接面(magnetic tunnel junction;MTJ)。

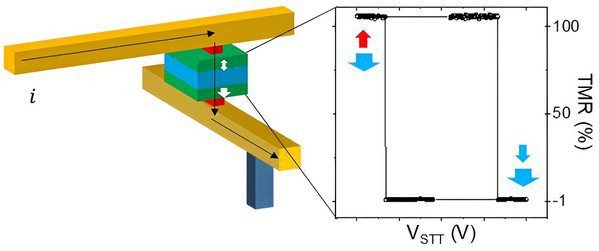

該接面包含一層鈷鐵硼(CoFeB)固定鐵磁層與一層鈷鐵硼(CoFeB)自由鐵磁層,兩者之間包含一層氧化鎂(MgO)介電薄膜。資料寫入透過轉換自由層的磁性來實現,自由層即MRAM記憶體單元的「儲存」層。資料讀取則是利用流經磁性穿隧接面的電流,測量該接面的磁阻大小來實現。

該穿隧磁阻(tunnel magnetoresistance;TMR)的高低由自由層與固定層的磁矩方向來決定,也就是說,如果兩個鐵磁層的磁矩平行且同向,則為1,若為平行但反向,則為0。

STT-MRAM與SOT-MRAM的主要差異在於寫入電流的幾何設計。STT-MRAM的寫入電流垂直於磁性穿隧接面,SOT-MRAM則採用平面設計,將寫入電流注入鄰近的元件底層(SOT layer)內,通常是諸如鎢(W)等重金屬。

因此,在SOT-MRAM設計中,讀取與寫入為不同路徑,進而大幅提升元件的耐久性與讀取穩定性。從平面方向注入電流還能解決STT-MRAM的開關延遲問題。2018年,imec首次展示可靠的SOT-MRAM元件,翻轉速度降至210ps,讀寫循環次數高達5x1010次以上,功耗僅需300pJ。

【欲閱讀更豐富的內容,請參閱2023.5第378期CTIMES雜誌】

延伸閱讀

贊助廣告

商品推薦

udn討論區

- 張貼文章或下標籤,不得有違法或侵害他人權益之言論,違者應自負法律責任。

- 對於明知不實或過度情緒謾罵之言論,經網友檢舉或本網站發現,聯合新聞網有權逕予刪除文章、停權或解除會員資格。不同意上述規範者,請勿張貼文章。

- 對於無意義、與本文無關、明知不實、謾罵之標籤,聯合新聞網有權逕予刪除標籤、停權或解除會員資格。不同意上述規範者,請勿下標籤。

- 凡「暱稱」涉及謾罵、髒話穢言、侵害他人權利,聯合新聞網有權逕予刪除發言文章、停權或解除會員資格。不同意上述規範者,請勿張貼文章。

FB留言